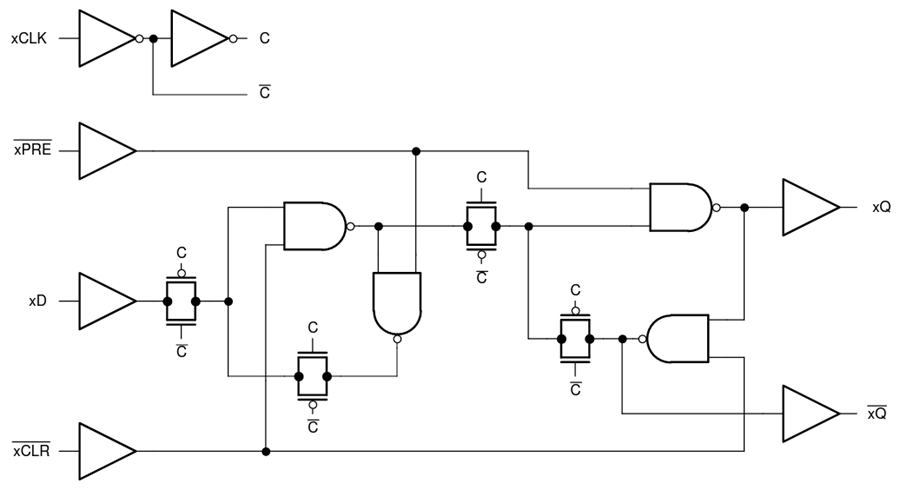

Los flip-flops duales tipo D SN74LV2T74/SN74LV2T74-Q1 de Texas Instruments contienen dos flip-flops independientes tipo D impulsados por flanco positivo. Un nivel bajo en la entrada preestablecida (PRE) establece la salida alta. Un nivel bajo en la entrada limpia (CLR) restablece la salida baja. Las funciones predefinidas y borradas son asíncronas y no dependen de los niveles de otras entradas. Cuando PRE y CLR están inactivos (alto), los datos en la entrada de datos (D) que cumplen con los requisitos de tiempo de configuración se transfieren a las salidas (Q, Q) en el flanco positivo del pulso de reloj (CLK). La activación del reloj ocurre a un nivel de tensión y no está directamente relacionada con el tiempo de subida de la señal del reloj de entrada (CLK). Después del intervalo de tiempo de espera, los datos en la entrada de datos (D) se pueden cambiar sin afectar los niveles en las salidas (Q, Q). El nivel de salida está referenciado a la tensión de suministro (VCC) y admite niveles CMOS de 1,8 V, 2,5 V, 3,3 V y 5 V.