Las características de los transistores de efecto de campo de potencia hacen que estos componentes sean ideales para la conmutación de cadenas intensas, o incluso como amplificadores. Sin embargo, estas características son diferentes de las de los transistores bipolares de potencia normalmente encontrados en circuitos que ejercen estas funciones. Conocerlas es fundamental para un proyecto bien hecho. El artículo que presentamos es una adaptación del Application Note AN-558 de National Semiconductor, que muestra cómo funciona y cómo debemos usar correctamente un FET de potencia (1999).

Los transistores de efecto de campo de potencia (Power MOSFETs) están disponibles básicamente en las versiones de enriquecimiento de canal N, doblemente difundidas.

Estos transistores pueden realizar las mismas funciones de los transistores bipolares de unión, excepto por el hecho de que son dispositivos controlados por tensión, y no por corriente.

El hecho de que los FET de potencia presenten una impedancia de entrada elevada y ser dispositivos con portadores mayoritarios de corriente hace que ellos no sufran los efectos del almacenamiento de portadores, deriva térmica o segunda barrera de ruptura.

FUNCIONAMIENTO

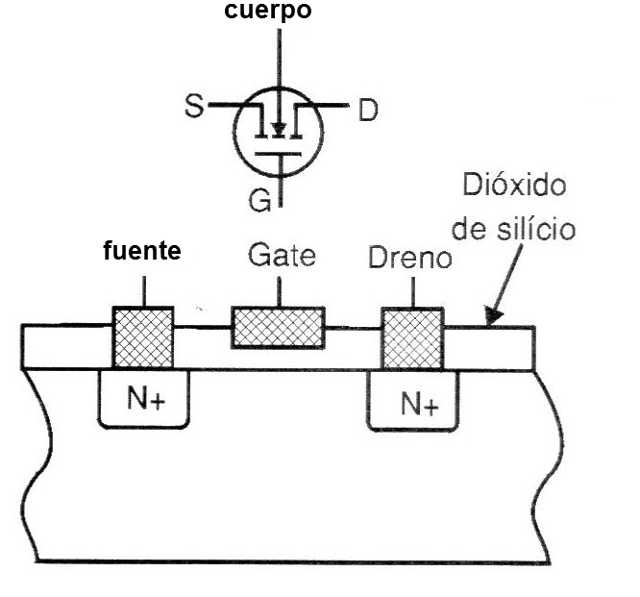

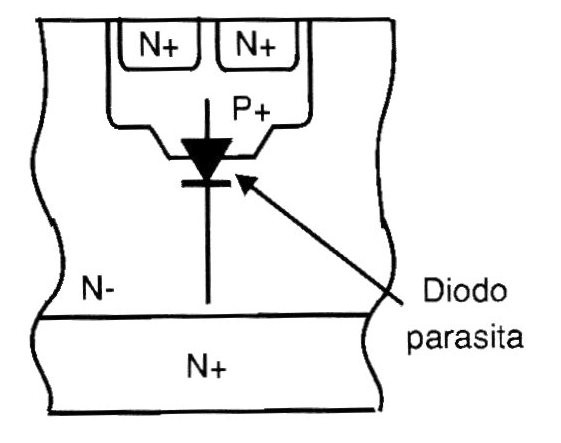

En la figura 1 tenemos la estructura básica de un MOSFET de potencia.

Sin polarización alguna aplicada a la compuerta (puerta G), ninguna corriente fluye entre el drenaje y la fuente (en ambas direcciones) porque siempre existe una unión PN bloqueando esta corriente.

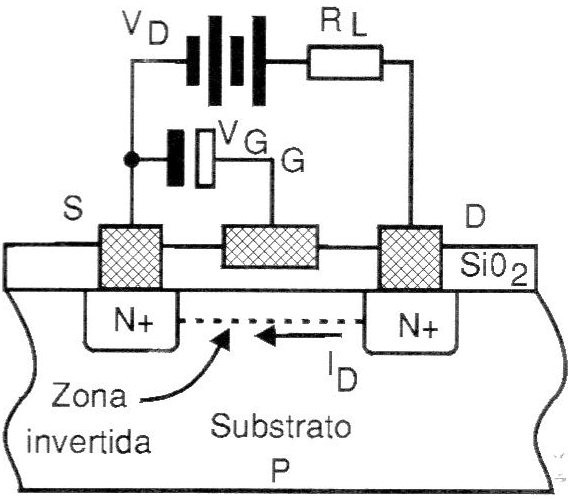

Cuando la compuesta se polariza en el sentido directo en relación a la fuente (S), como se muestra en la figura 2, los huecos libres que funcionan como portadores de carga en la capa epitaxial P se repiten lejos del área de la coma creando un canal por donde pueden fluir los electrones de la fuente para el dren.

Obsérvese que, siempre que los huecos hayan sido repelidas del canal de comporta, los electrones se convierten en portadores mayoritarios de cargas por defecto.

Este modo de operación se llama "enriquecimiento", pero es más fácil pensar en el modo de funcionamiento como si el dispositivo se mantuviera normalmente apagado.

El modo de operación opuesto se denomina "deplexión", que lleva a un dispositivo que permanece normalmente conectado (ON).

El transistor tomado como ejemplo es del tipo "Lateral MOSFET" y tiene ventajas y desventajas.

Las ventajas son:

1. Requiere muy poca potencia de conducción. No hay circulación de corriente por la compuesta una vez que la pequeña capacitancia que r existe en este electrodo sea cargada.

2. Las velocidades de conmutación son elevadas, ya que los electrones pueden comenzar a circular desde el desagüe hasta la fuente tan pronto como el canal se abra. La anchura del canal es proporcional a la tensión aplicada a la compuerta y se cierra tan pronto se quita la tensión. No existe, por lo tanto, efecto de tiempo de almacenamiento que ocurre con transistores bipolares.

Las desventajas principales son:

1. Canales de alta resistencia. En la operación normal, la fuente es eléctricamente conectada al sustrato. Sin polarización, la región de deplexión se expande hacia fuera del dren N +, con un formato pseudo-hemisférico. La longitud del canal no se puede hacer menor que la anchura mínima de depleción necesaria para soportar la tensión especificada para el dispositivo.

2. La resistencia del canal puede reducirse mediante la utilización de canales más amplios, pero esto aumenta el costo del dispositivo por requerir más silicio. Esta característica también reduce la velocidad de conmutación del dispositivo por el aumento de la capacidad de conducción.

3.

MOSFETS VERTlCALES

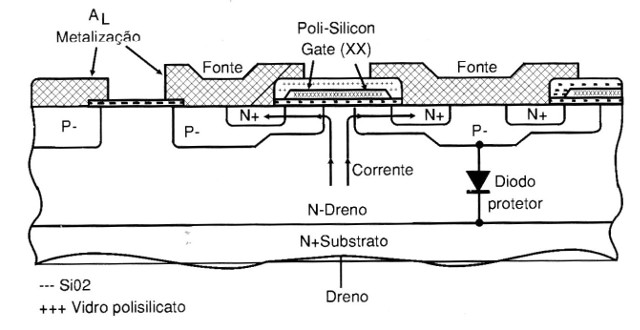

Los MOSFETS verticales (también llamados DMOS) tienen la estructura mostrada en la figura 3.

El camino de la corriente es creado por la inversión de la capa P por debajo de la compuesta a través de un método igual al de los MOSFETs laterales.

La corriente de la fuente fluye por debajo del área de la compuesta y verticalmente a través del dreno, extendiéndose por debajo a medida que fluye.

Un MOSFET típico consiste en muchos miles de fuentes N + que conduce en paralelo.

Este tipo de arquitectura hace posible geometrías de proyectos que presentan bajas resistencias en el estado de conducción (Rds (on)) para la misma tensión de bloqueo, y alta velocidad de conmutación en comparación con los FET laterales.

Hay muchos modos de proyectar el MOSFET vertical, tales como ranuras en V, en U, y muchas formas de fuentes como cuadradas, triangulares, hexagonales, etc.

Todos los MOSFETS comercialmente disponibles con tensiones superiores a 300 V se fabrican con una estructura similar a la mostrada en la figura 3.

Las principales consideraciones que determinan la geometría de la fuente son la ds (on), capacitancia de entrada, tiempo de conmutación y transconductancia.

El Diodo Parasita

Las primeras versiones de los MOSFET eran muy susceptibles a la tensión de ruptura debido a transitorios de tensión, y también tenían una tendencia a conectarse bajo un crecimiento muy rápido de la tensión de drenaje / fuente (dV / dt), ambos resultando en fallas catastróficas.

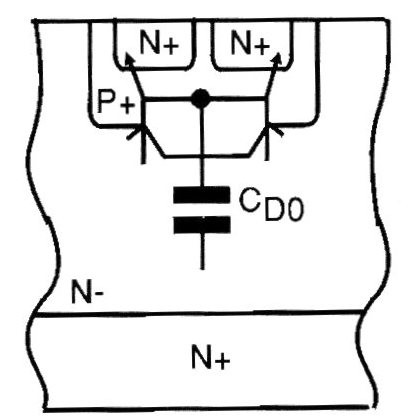

El problema de la tendencia a conectar bajo altas tasas de crecimiento de la tensión de entrada (dV / dt) ocurre debido al transistor parasita NPN incorporado a la estructura del MOSFET, como se muestra en la figura 4a.

La corriente que fluye para cargar la capacitancia de la unión Cdg funciona como una corriente de base para este transistor tendiendo a llevarlo a la conducción.

La acción del transistor NPN parásito puede ser suprimida colocando en corto la fuente N + al cuerpo P + a través de la metalización de la fuente.

Esto crea un diodo PN inherente conectado en anti-paralelo al transistor MOSFET, como muestra la figura 4b.

Debido a la gran superficie de la región de la unión de este diodo, su capacidad de corriente y también su capacidad de disipación de calor son las mismas del propio MOSFET.

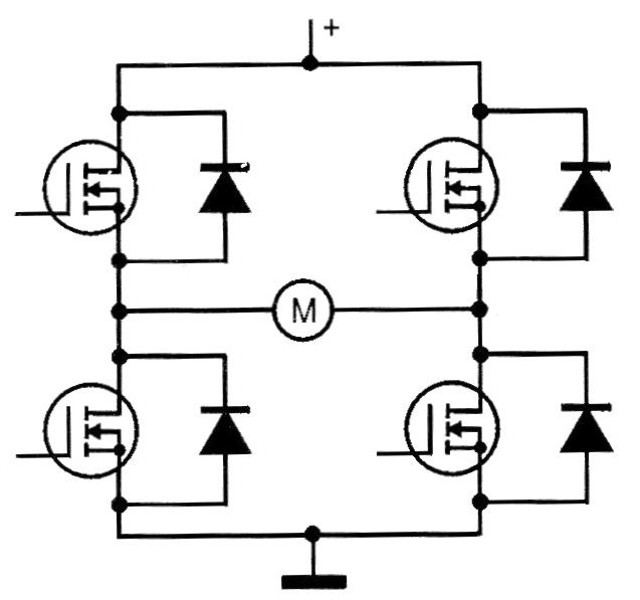

Este diodo parásito tiene como características un largo tiempo de recuperación reversa y una corriente reversa de recuperación grande debido al tiempo de duración de los portadores minoritarios de corriente en la capa de drenaje N - lo que hace interesante su uso en aplicaciones para frecuencias bajas como, por ejemplo, por ejemplo, en el control de motores, mostrado en la figura 5.

Sin embargo, en las aplicaciones de altas frecuencias el diodo parásito necesita ser ayudado con la conexión de un diodo ultra-rápido conectado en paralelo externamente al transistor para que el diodo parásito no conmute solo.

CONTROLANDO EL MOSFET

Una de las mayores ventajas del Power MOSFET es su alta velocidad de conmutación.

La corriente de drenaje es proporcional a la tensión de conducción de tal forma que un dispositivo teóricamente perfecto puede conmutar en tiempos entre 50 y 200 ps (picossegundos), tiempo que los portadores de carga tardan en fluir del fluido de drenaje a la fuente.

Dado que el MOSFET es un dispositivo de portadores mayoritarios de carga, una de las razones por las que puede tener mejor rendimiento que un transistor bipolar equivalente, es que el tiempo de desconexión no es retrasado por el almacenamiento de portadores minoritarios de carga en la base.

Un MOSFET empieza a apagar tan pronto la tensión de conducción cae por debajo de su umbral.

PROCEDIMIENTO DE DISPARO

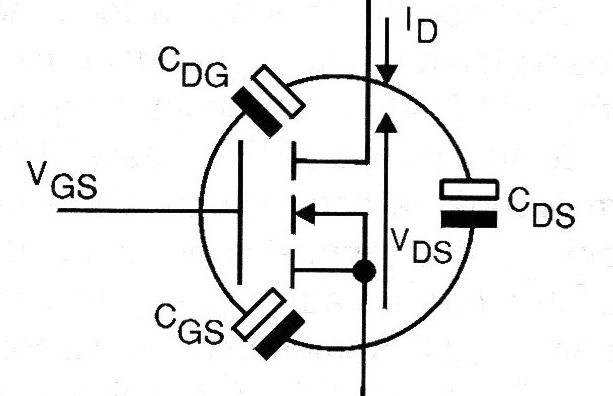

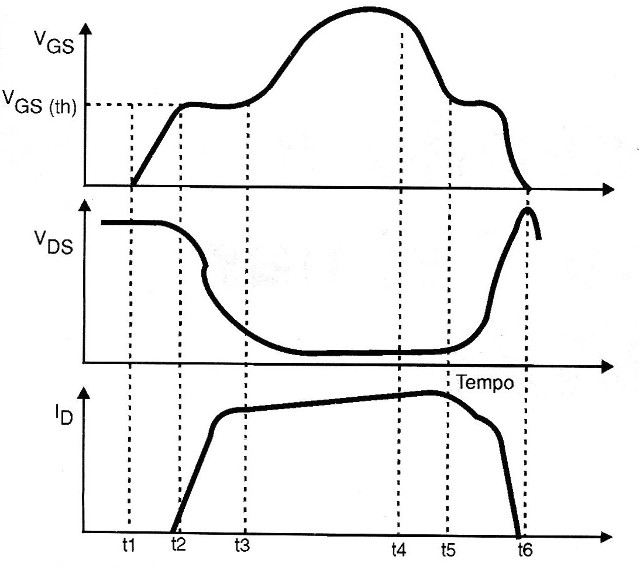

La figura 6a muestra un modelo simplificado de las capacitancias parásitas que existen en un Power MOSFET y las formas de onda de la tensión de conmutación de una carga resistiva.

Hay varios fenómenos que ocurren durante la conmutación cuando el transistor se conecta, y que se pueden entender a partir de la misma figura.

El intervalo de tiempo t1

El tiempo de retardo inicial td (on) ocurre debido al intervalo de tiempo que tarda Vgs para crecer exponencialmente hasta la tensión umbral Vgs (th).

A partir de la figura 6b, la constante de tiempo puede ser dada como

Rs x Cgs.

Típicamente, el tiempo de conexión para los transistores lRF33O de National es dado por:

td (on) = Rs x Cgs x ln (1 - Vgs (h) / Vpk)

Para un generador de señales con impedancia asumida en Rs de 50 ohms y Cgs de 600 pF, el tiempo td será de 11 ns.

Tenga en cuenta que desde que la impedancia de la fuente de señal aparece en la ecuación, es muy importante observar las condiciones de prueba usadas cuando se miden los tiempos de conmutación.

Físicamente se puede medir sólo la capacitancia de entrada Cgs, que es dada por Cgs en paralelo con Cdg.

Incluso considerando que Cgsg, esta última capacitancia es sometida a una variación mucho mayor de tensión y por lo que no puede ser descuidada.

La carga y descarga de Cgs es análoga al efecto 'Miller' que ocurre en las válvulas al vacío y que domina el siguiente tiempo de conmutación:

t2

A partir del instante en que la tensión Vgs alcanzó el punto de umbral, el MOSFET comienza a drenar una corriente creciente de la carga y Vds disminuye.

Cgd debe, entonces, no sólo descargar como también aumentar de valor, pues su capacitancia es inversamente proporcional a Vgd, más precisamente dada por la fórmula abajo:

Cdg = Cdg (o) l (Vdg) n

A menos que la etapa de excitación pueda suministrar rápidamente la corriente necesaria para la descarga de Cdg, la caída de tensión puede reducirse con una correspondiente prolongación del tiempo de conmutación.

Intervalo de tiempo:

t3

En este intervalo, el MOSFET está ahora en el estado ON y la tensión de conducto puede estabilizarse en el valor normal de excitación.

Intervalo de tiempo:

t4

El tiempo de desconexión ocurre en el orden inverso.

Vgs debe caer de nuevo al valor del umbral antes de que Rds (on) empiece a aumentar.

Tan pronto como vds comienza a aumentar, el efecto Miller debido a Cdg se reanuda, y esto impide que el crecimiento de Vds así como Cdg se recargue hasta Vcc.

CONCLUSIÓN

Dependiendo de las aplicaciones específicas, todos estos efectos deben ser considerados.

Esto hace que se requieran configuraciones especiales, según las aplicaciones.