La utilización cada vez mayor de dispositivos de bajo consumo, principalmente los microcontroladores, está exigiendo circuitos de apoyo compatibles con su baja tensión de alimentación, predominantemente de 3,3 V. Así, las familias lógicas tradicionales TTL y CMOS ya no sirven para la elaboración de circuitos que interfieren con los microcontroladores y otras aplicaciones. Para atender la demanda de circuitos lógicos que interceptan con microcontroladores y otras aplicaciones de 3,3 V muchos fabricantes poseen lógicas específicas, familias de baja tensión y bajo consumo como la que abordamos en este artículo.

Con la introducción de la familia LVC, Texas Instruments inició una nueva era de componentes rumbo a mayores velocidades, menor disipación y equipamientos de menor tamaño con lógicas como LVC, LV y ALVC.

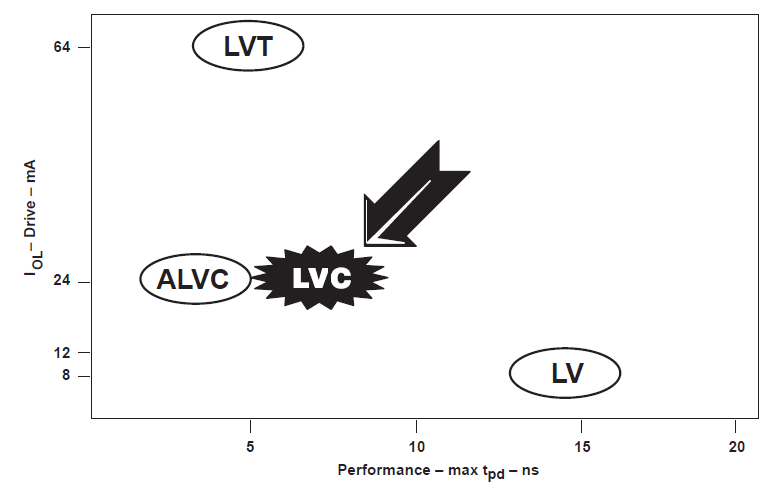

La familia lógica LVC se caracteriza por ser tolerante a la alimentación de 5 V, con una velocidad de 6,5 ns (tiempo de propagación) y capacidad de suministrar corrientes de 24 mA.

En realidad, según Texas Instruments indica, las familias alternativas de baja tensión poseen velocidades y capacidades de corriente diferentes, que pueden ser elegidas conforme a la aplicación, de la misma forma que lo hacemos con las sub-familias TTL (que también fueron creadas por Texas Instruments) . El gráfico de la Guía de selección de Texas muestra las diferencias que se muestra en la figura 1.

Una posibilidad para utilizar circuitos lógicos en circuitos de 3,3 V es aprovechar dispositivos de 5 V, pero en este caso su velocidad se reduce.

Así, la LVL consiste en una mejora de estos dispositivos de modo que no pierdan sus características de rendimiento.

Con la utilización de una tensión más baja de alimentación, el consumo disminuye en una proporción directa al cuadrado de su valor de reducción. Con ello tenemos también menor producción de calor además de otros beneficios.

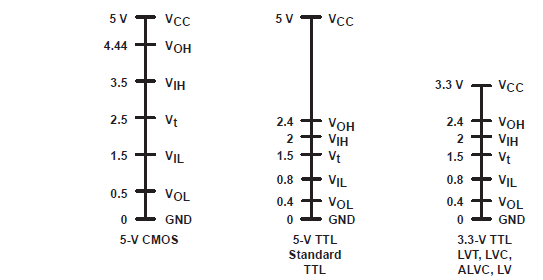

En la interfaz de circuitos lógicos de 5 V con circuitos de 3,3 V debemos considerar las bandas reconocidas de los niveles, de forma que los lectores pueden profundizarse mejor a través de nuestro curso de electrónica digital y analizado la tabla que damos a continuación.

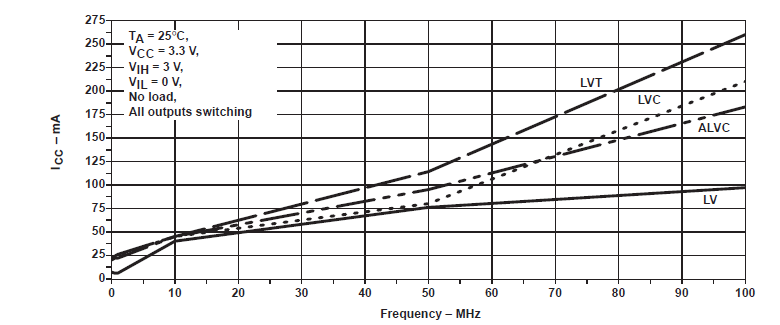

En la figura 2 tenemos los gráficos de conmutación de las lógicas de 5 V y de las lógicas de 3,3 V.

Así, en la interfaz de las diversas lógicas tenemos 4 casos a ser considerados:

a) Dispositivo TTL de 5 V que excita un TTL de 3,3 V

En este caso, como podemos ver por los gráficos, los niveles de conmutación de los dispositivos LLT de 5 V son los mismos de los dispositivos LVC de 3,3 V. Dado que los dispositivos LVC son tolerantes a una tensión de 5 V, no hay necesidad de ningún recurso la interfaz entre estas dos lógicas, como muestra la figura 3.

Una tecnología adicional (CBT) puede ser usada para transformar TTL de 5 V y dispositivos de 3,3 V que no sean tolerantes a 5 V.

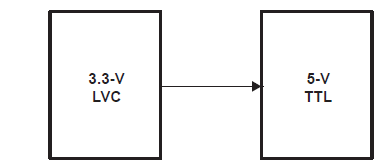

b) Dispositivo TTL de 3,3 V (LVC) excitando TTL de 5 V

En este caso también, como los niveles lógicos de disparo son los mismos, no hay necesidad de ningún dispositivo adicional en la interfaz. Puede ser directo, como se muestra en la figura 4.

c) Dispositivo CMOS de 5 V excitado TTL de 3,3 V (LVC)

En este caso, hay dos patrones que no se casan. Con un análisis mejor de los niveles de conmutación VOH y VOL del CMOS de 5 V y el VIH y VIL del LVC de 3,3 V, por la figura 2 vemos que a pesar de la disparidad, un dispositivo de 5 V tolerante a los 3,3 V funcionará con niveles CMOS de entrada de 5 V. Con un LVC tolerante a los 5 V una configuración CMOS de 5 V que excita un LVC de 3,3 V es posible.

d) TTL de 3,3 V (LVC) que excita CMOS de 5 V

En este caso tenemos lógica TTL de 3,3 V (LVC) excitando un CMOS alimentado por 5 V. Hay algunos niveles diferentes estandarizados en estas dos lógicas que pueden significar una interferencia en la interfaz. Si observamos la figura 2 vemos que el VOH para un dispositivo LVC de 3,3 V es 3,4 V (niveles altos de salida de hasta 3,3 V), mientras que el mínimo requerido de VIH para un dispositivo CMOS de 5 V es 3,5 V.

Por lo tanto, excitar un dispositivo CMOS de 5 V con un LVC de 3,3 V (u otro dispositivo de 3,3 V) es imposible, incluso como máximo de VOH de 3,3 V, el VIH mínimo de 3,3 V nunca se obtiene. Para acomodar este hecho, Texas Instruments diseñó una serie de dispositivos que amplían esa posibilidad.

Estos dispositivos tienen un lado alimentado por 3,3 V y el otro por 5 para hacer el matrimonio de los niveles lógicos.

En el gráfico mostrado en la figura 7 vemos que las diversas familias de baja tensión poseen comportamientos diferentes en relación a la frecuencia, lo que debe ser considerado en los proyectos.

Para saber más, Texas Instruments cuenta con el scba010.pdf un documento en el que detalla las características de los componentes de esta familia haciendo comparaciones.

Para obtener este documento acceda a: http://www.ti.com/lit/an/scba011/scba011.pdf

Las Familias Lógicas LVC y LV

Así como otros fabricantes Texas Instruments dispone de una enorme cantidad de dispositivos lógicos de las familias LVC y LV para transición de 5 V a 3,3 V ambas de baja tensión CMOS.

La familia LVC es una respuesta a los proyectistas que desean proyectar con lógica de 3,3 V, pero con tolerancia a 5 V y un tiempo de propagación de 3,8 ns y corriente de salida de 24 mA. Texas tiene más de 60 dispositivos en esta familia.

La familia LV es una solución de bajo costo de 3,3 V, con un tiempo de propagación de 8,3 ns y 8 mA de corriente de salida.

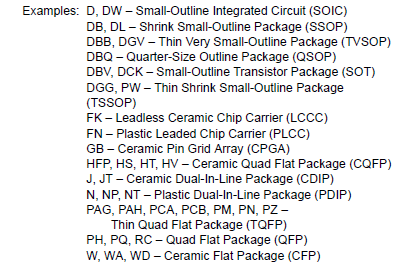

Las envolturas disponibles son SOIC, SSOP, TSSOP y TVSOP.

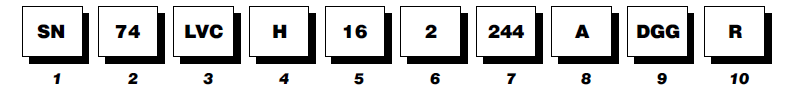

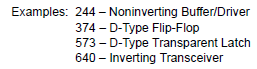

A continuación tenemos una tabla de Texas Instrruments que indica cómo se realiza la identificación con componente.

1. Prefijo indicando el fabricante

2. Rango de temperatura

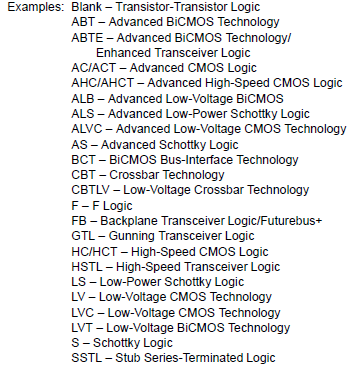

3. Familia

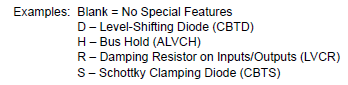

4. Destacados especiales

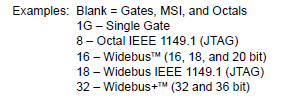

5. Ancho de Bit

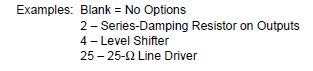

6. Opciones

7. Función

8. Revisión

9. Envoltorios

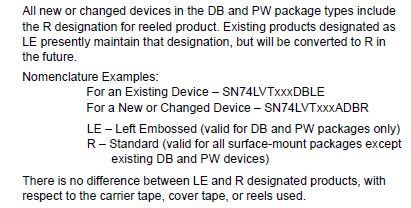

10. Cinta o rollo

Texas Instruments ofrece un databook completo de sus componentes LVC y LV con 915 páginas que se pueden descargar en formato PDF en: http://www.ti.com/lit/ug/scbd152b/scbd152b.pdf

Para los proyectistas que trabajan con matriz de contacto es importante observar que una buena parte de los dispositivos está disponible en envoltorios J (Dual in Line) con dimensiones que permiten el encaje directo.