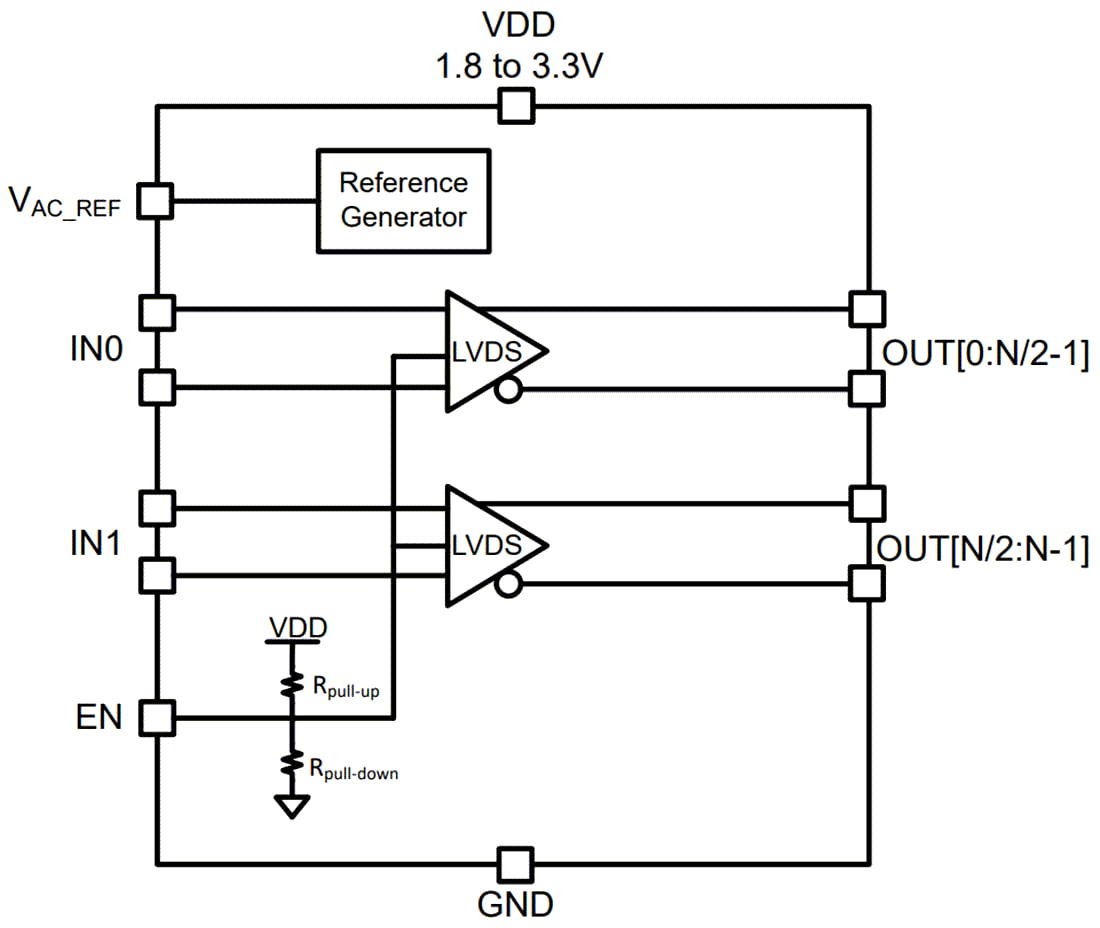

El búfer LVDS de bajo jitter aditivo LMK1D210x de Texas Instruments distribuye dos entradas de reloj (IN0 e IN1) para un total de hasta 8 pares de salidas de reloj LVDS diferenciales (OUT0, OUT7) con una distorsión mínima para la distribución del reloj. Cada bloque de búfer consta de una entrada y hasta 4 salidas LVDS. Las entradas pueden ser LVDS, LVPECL, HCSL, CML o LVCMOS. El LMK1D210x está diseñado específicamente para impulsar líneas de transmisión de 50 Ω. En caso de conducir las entradas en modo de un solo extremo, se debe aplicar el voltaje de polarización apropiado al pin de entrada negativo no utilizado.