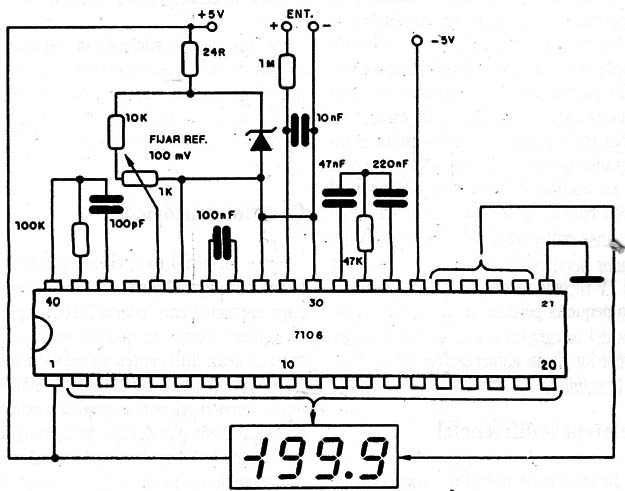

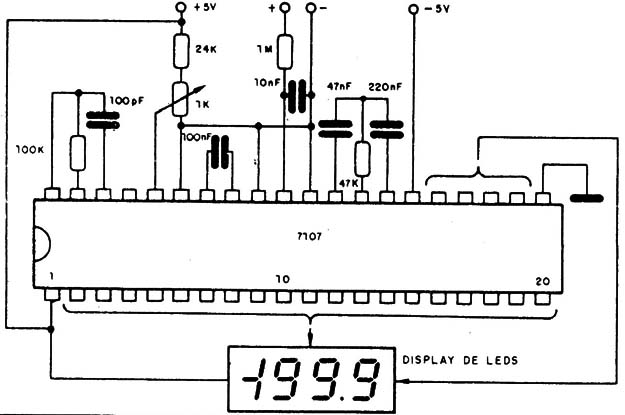

Presentamos en este artículo dos conversores A/D (analógico/digital) de 3 y1/2 dígitos, de bajo consumo, y que se prestan para una infinidad de proyectos de instrumentación que van desde voltímetros y termómetros, hasta configuraciones mas complejas, como por ejemplo, un multímetro. El 7106 está proyectado para excitar displays de cristal líquido, mientras que el 7107 está proyectado para excitar displays de diodos emisores de luz, pera las características generales de los dos son las mismas, de ahí la posibilidad de un tratamiento en un único artículo. Además de los datos técnicos de estos integrados, le proporcionará circuitos explicativos que fueron elaborados en base a la in formaciones del fabricante.

Los circuitos integrados lCL7106 y ICL7107 consisten en conversores analógicos / digitales de alto rendimiento y bajo consumo, capaces de proporcionar una salida de 3 y 1/2 dígitos directamente para displays de cristal líquido (7106) y de diodos emisores de luz (7107). Estos integrados incorporan todos los elementos para proporcionar una salida digital a partir de una entrada analógica, tales como decodificadores, drivers, referencias, clock, etc.

Esos integrados proporcionan juntos una combinación sin precedentes de precisión, versatilidad y economía. La precisión tiene como punto alto la polarización de entrada de 10 pA (máx.) y el cero automático para menos de 10 uV.

La versatilidad puede ser destacada en la posibilidad de uso de entrada diferencial. Finalmente, la economía está en la prescindencia de fuentes complejas, y el reducido número de componentes externos para excitación del display y para la entrada.

Entre las características principales destacadas por el fabricante tenemos:

Garantía de lectura "cero" con 0 V de entrada en todas las escalas.

Polarización real de cero para detección de nulo.

Corriente de entrada típica: 1pA. Excitación directa de los displays, sin necesidad de componentes externos.

Bajo ruido: menos que 15uVpp.

Referencia y clock incorporados.

Baja potencia de disipación: menos de 10 mW (tip.)

No necesita circuitos activos externos.

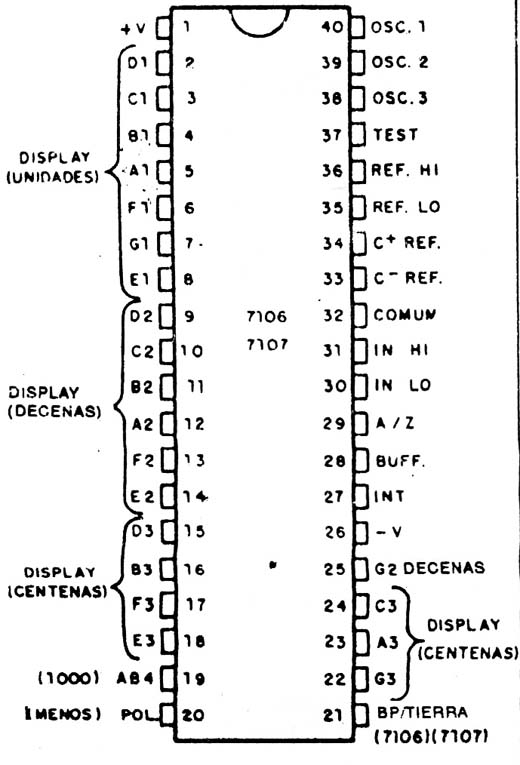

En la figura 1 tenemos la cubierta de 40 pinos (DIL) con la identificación de los terminales para los integrados.

Máximos absolutos

Tension de alimentación:

ICL7106 +V a -V: 15V

ICL7107 +V a tierra: +6V

ICL7107 -V a tierra: -9V

Disipación de potencia: 800mW

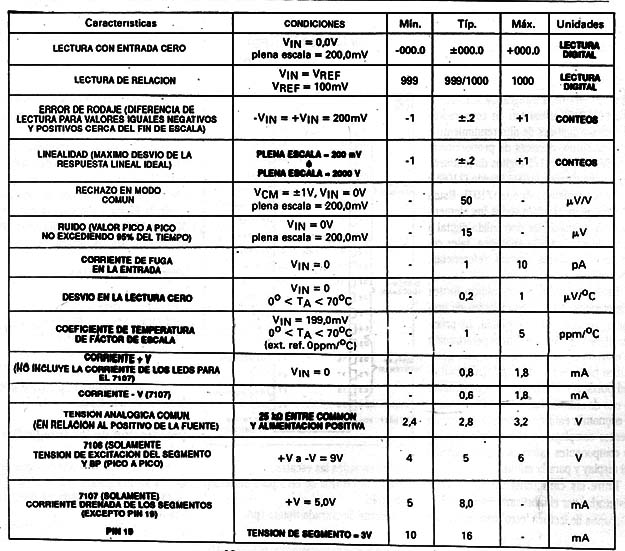

Las características eléctricas pueden observarse en la tabla.

Descripción de los integrados

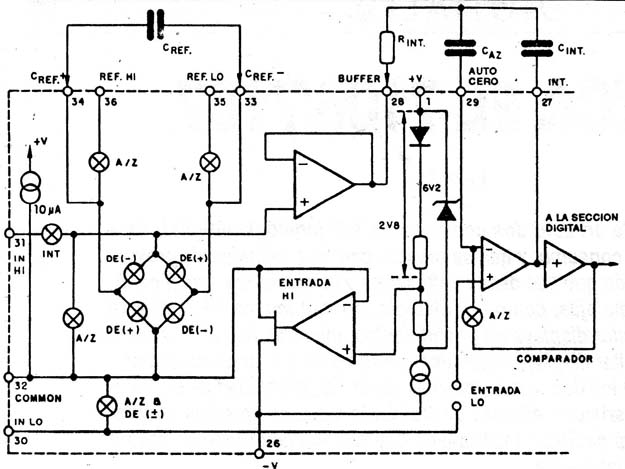

En la figura 2 tenemos el sector analógico de los integrados 7106 y 7107.

Cada ciclo de medida es dividido en tres fases:

(1) autocero (A/Z), (2) integración de la serial (INT) y (3) desintegración (DE).

1 - Fase autocero

Durante esta fase ocurren tres hechos. En primer lugar las entradas HI y LO son desconectadas de los pines, e internamente, son cortocircuitadas al "COMMON" analógico.

En segundo lugar, el capacitor al que nos referimos es cargado con la tensión de referencia. En tercer lugar, un eslabón de realimentación es cerrado entorno del sistema para cargar el capacitor de autocero CAz para compensar las tensiones offset en el amplificador, integrador y comparador.

A partir del momento en ("16 el comparador es incluido en el eslabón de realimentación, la precisión A-Z queda limitada solamente por el nivel de ruido del sistema.

De cualquier forma, el offset referido a la entrada es menor que 10 uV.

2 - Fase de integración de la señal

Durante la integración de la serial, el eslabón de realimentación autocero es abierto, por la remoción interna del corto, y las entradas internas HI y LO son conectadas a los pines externos. El conversor integra, entonces, la tensión diferencial entre la entrada IN HI e IN LO durante un intervalo de tiempo fijo.

Esa tensión diferencial puede ser aplicada de modo común, con 1V menos (como máximo) que la tensión de la fuente.

Si no se hace esto, la señal de entrada no tendrá ningún retorno en relación a la fuente de alimentación del conversor. La entrada IN LO puede ser conectada directamente al "COMMON" para establecer una operación correcta en modo común.

En el final de esta fase, la polaridad de la señal integrada estará determinada.

3 - Fase de desintegración

La entrada DO es internamente conectada al "COMMON" analógico y la entrada HI es conectada al capacitor de referencia previamente cargado.

El circuito en el interior del chip asegura la conexión del capacitor con la polaridad correcta, de modo de llevar la salida del integrado al retorno a cero.

El tiempo requerido para que la salida retorne a cero es proporcional a la señal de entrada.

Específicamente la lectura digital mostrada es 1000 (Vin/Vref).

Entrada diferencial

La entrada puede aceptar tensiones de cualquier valor dentro de la banda descripta de modo común del amplificador de entrada, o específicamente de 1 V por encima de la fuente negativa hasta 0,5V por debajo de la tensión de la fuente positiva.

En esa banda el sistema posee un rechazo en modo común (CMRR) de 86dB típicamente. Mientras tanto, como el integrador también oscila con la tensión en modo común, se debe tener cuidado para asegurar que la salida del integrador no se sature.

La condición más desfavorable puede ser una gran tensión en modo común positiva con una tensión diferencial negativa próxima al fondo de escala. La señal en la entrada negativa excita el integrador positivo cuando la mayor parte de su oscilación haya sido usada en el modo común de tensión.

Para esas aplicaciones críticas, las oscilaciones del integrador pueden ser reducidas a menos de los 2V recomendados de fondo de escala, con pequeña perdida de precisión. La salida del integrador puede oscilar en 0,3V alrededor de la alimentación sin perdida de linealidad.

Referencia diferencial

La tensión de referencia puede ser generada en cualquier parte de la fuente de alimentación del conversor. La principal fuente de error en modo común es una perdida de tensión, causada por problemas de fugas o ganancia de carga en el capacitor.

Si hubiera una gran tensión en modo común, el capacitor de referencia puede ganar carga (aumentando la tensión) cuando se le solicita desintegrar una señal positiva, pero puede perder carga (disminuyendo la tensión) cuando se le solicita desintegrar una señal negativa.

Esta diferencia en la referencia + o - en la tensión de entrada puede resultar en un error.

Mientras tanto, eligiendo un capacidad de referencia suficientemente grande en relación a la capacidad parasita, ese error puede ser reducido a menos, de 0,5 del conteo, en las condiciones mas desfavorables.

Common analógico

Este terminal es incluido primariamente para fijar el punto de modo común para operación con batería (7106) o para cualquier sistema en que las señales de entrada sean fluctuantes en relación a la fuente de alimentación. El pin COMMON fija la tensión en que se tiene aproximadamente 2,8V por debajo de la tensión positiva de la alimentación.

Este valor es seleccionado en función de la tensión de una batería de 6V cuando está descargada. Mientras tanto, la entrada COMMON analógico tiene algunos atributos de una tensión de referencia. Cuando la tensión de alimentación es suficientemente alta para hacer que el zener entre en acción (mayor que 7V), la tensión COMMON presentará un coeficiente de baja tensión (0,00 1%); baja impedancia (100ohm aprox.) y coeficiente de temperatura típicamente menor que 8oppm por ºC.

Las limitaciones de una referencia incorporada al chip deben ser reconocidas.

En el caso del 7107, el calor interno generado por los drivers de los LEDs pueden ocasionar alguna degradación en el rendimiento. Debido a su alta resistencia térmica, la cubierta plástica presenta desventajas en relación a la cerámica.

La combinación del Coeficiente de Temperatura de Referencia, disipación del chip y resistencia térmica de la cubierta puede aumentar el ruido en el final de la escala de 25uV hasta uVpp. También la linealidad, en el caso de encendido de todos los segmentos ( 1000 = 20 segmentos activados), para el encendido del mínimo de segmentos (1111 = 8 segmentos) puede verse afectada.

Dispositivos con una referencia TC positiva pueden necesitar de diversos ciclos de conteo para salir de una condición de sobrecarga. Por ese motivo es que la sobrecarga se produce en la condición de baja disipación, con los tres dígitos menos significativos apagados.

Similarmente, las unidades con un TC negativo pueden aparecer y desaparecer en función de condiciones de sobrecarga y no sobrecarga. Si se usara una referencia externa, todos esos problemas desaparecen.

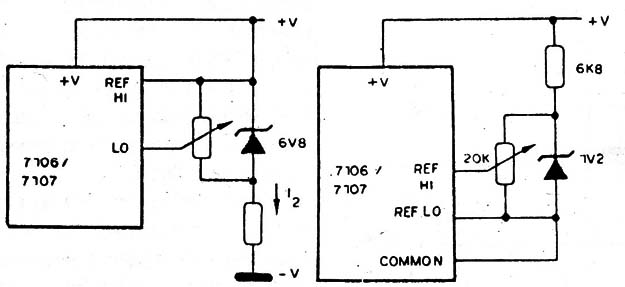

El 7106, con su disipación muy pequeña, no sufre esos problemas. En los dos casos, una referencia externa puede ser agregada fácilmente, como muestra la figura 3.

La entrada COMMON analógico también puede ser usada como retorno del nivel LO de entrada durante el autocero y desintegración.

Si (IN LO) fuera diferente de COMMON analógico, se manifiesta en el sistema una tensión de modo común, debiendo tomarse precauciones con su acción en relación al CMRR del conversor. Mientras tanto, en algunas aplicaciones (IN LO) se puede mantener en un nivel fijo de tensión conocida (tensión de alimentación por ejemplo).

En esa aplicación, la entrada COMMON analógica puede ser conectada al mismo punto, quitándose entonces la tensión en modo común del conversor. Si la referencia pudiera ser establecida convenientemente en función de la entrada COMMON, eso también ayudará a eliminar la tensión en modo común del sistema de referencia.

En el interior del CI, la entrada COMMON analógica es conectada a un transistor de efecto de campo de canal N, que puede drenar 30 mA o más de corriente, para mantener la tensión de referencia 2,8V por debajo de la tensión de alimentación.

Mientras tanto, existe solamente 10uA de la fuente de corriente para ese transistor, lo que significa que el COMMON puede ser fácilmente conectado a una fuente de tensión más negativa, sin peligro de afectar la referencia interna.

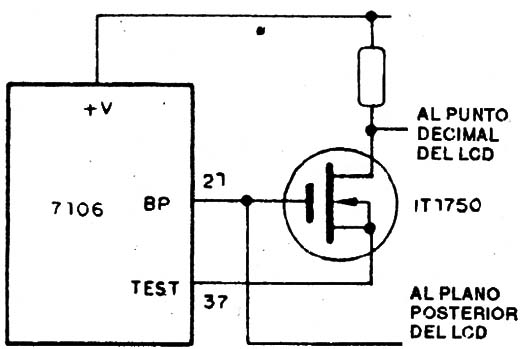

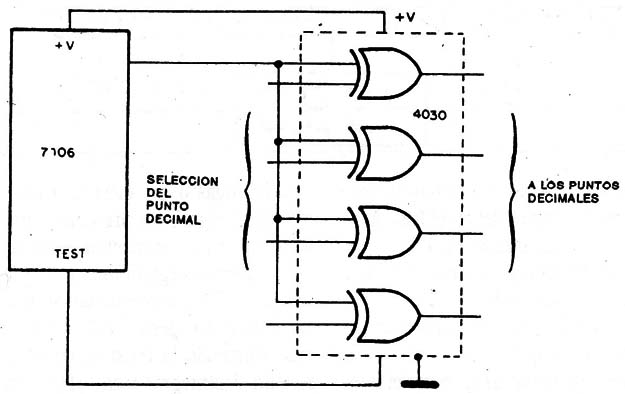

Test

El pin TEST sirve para dos funciones. En 7106 está acoplado a la fuente interna, con generación digital a través de un resistor de 500 ohm. Eso significa que puede ser usado como fuente negativa para drivers de segmentos adicionales externos, como por ejemplo puntos decimales u otros que el proyectista quiera incluir.

En las figuras 4 y 5 tenemos aplicaciones en que la corriente no debe superar 1mA.

La segunda función es un "lamp-test". Cuando TEST es llevado al nivel HI(+V) to- dos los segmentos son activados y el display debe presentar "1888".

El pin TEST puede drenar alrededor de 10mA en estas condiciones.

Sección digital

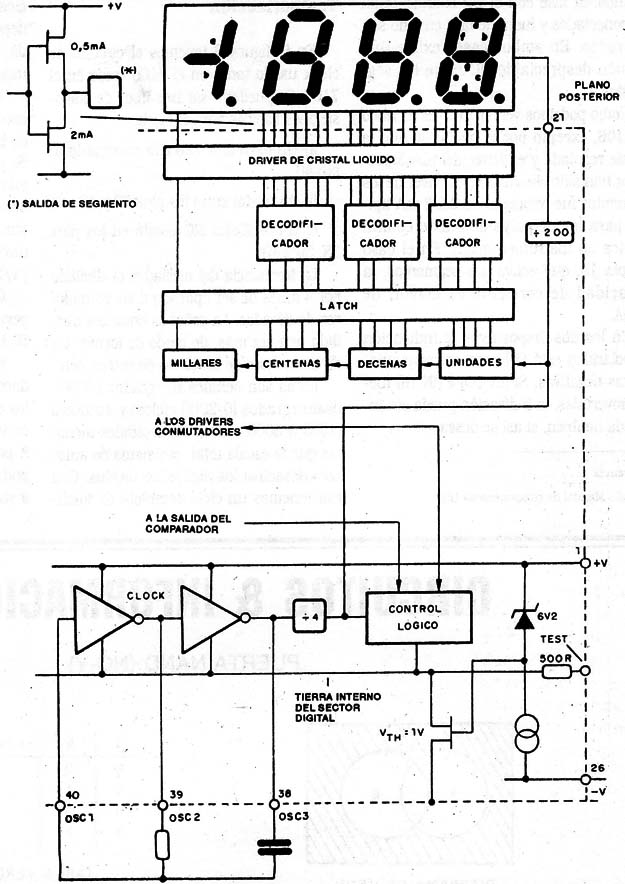

En las figuras 6 y 7 tenemos el sector digital del 7106 y 7107 respectivamente.

En el 7106 tenemos una tierra digital generada a partir de un zener de 6V y un Seguidor de fuente. Esta fuente es firme para poder absorber los efectos de las capacitancias relativamente altas que provocan Corrientes intensas, cuando el plano posterior del display tiene las tensiones de conmutación aplicadas al mismo.

La frecuencia del plano posterior (BP) es la frecuencia del clock dividida por 800. Para tres lecturas por segundo eso significa una onda cuadrada de 60Hz con amplitud nominal de 5V.

Los segmentos son excitados en la misma frecuencia y amplitud, estando en fase con el BP cuando están desconectados y fuera de fase cuando son activados. En ambos casos existe una tensión despreciable DC entre los segmentos.

Como podemos ver, el 7107 es idéntico al 7106, excepto por el hecho de que la fuente regulada y el driver del plano posterior han sido eliminados, el driver de los segmentos fue reforzado de 2 a 8 mA típicos para los displays de ánodo común usados en instrumentación.

En el caso del pin 19, que activa dos segmentos, la capacidad de corriente es mayor, de 16mA

En los dos dispositivos la indicación de polaridad está ON para entradas analógicas negativas. Si (IN LO) e (IN HI) fueran invertidas, la indicación puede ser invertida también, si así se desea.

Temporización

En la figura 8 tenemos el circuito de clock usado tanto en el 7106 como en el 7107. Se pueden usar tres tipos de disposiciones básicas para el clock:

a) Un oscilador externo conectado al pin 40.

b) Un cristal entre los pinos 39 y 40.

c) Un oscilador RC usado en los pinos 38, 39 y 40.

La frecuencia del oscilador es dividida por 4 antes de ser aplicada a los contadores de décadas. La señal es entonces dividida una vez más, de modo de formar las diversas fases de los ciclos de conversión.

Estas son señales integrados (1000), desintegrados (0-2000 ciclos) y autocero (1000 a 3000 ciclos). Para señales menores que la escala total, el sistema de autocero desactiva los dígitos no usados. Con eso tenemos un ciclo completo de medición de 4000 (16.000 pulsos de clock), independientemente de la tensión de entrada. Para 3 lecturas por segundo, se puede usar un oscilador de 48 kHz.

Para conseguir un máximo rechazo de captación de 60 Hz, el ciclo de integración de la señal debe ser un múltiplo de 60 Hz.

Se pueden seleccionar frecuencias del oscilador de 240 kHz, 120 kHz, 60 kHz, 48kHz, 40kHz, 33 y 1/2kHz, etc. Para rechazo de 50 Hz, las frecuencias del oscilador pueden ser 200kHz, 100kHz, 66 kHz, 50kHz, 40kHz, etc.

Observe que la frecuencia de 40 kHz permite el rechazo tanto de 60 como de 50 Hz.

En la segunda parte de este artículo daremos el modo de hacer la selección de los componentes externos, además de circuitos aplicativos con los dos conversores.

A partir de los circuitos descriptos usted podrá, con facilidad, proyectar diversos instrumentos digitales.