Las características de los amplificadores operativos con transistores CMOS permiten que estos componentes lleven muchas ventajas en aplicaciones donde normalmente se utilizarían amplificadores operativos comunes. Texas lnstruments posee en Brasil una amplia gama de amplificadores operativos con transistores de efecto de campo en la entrada, como por ejemplo los de la serie TLC. Lo que hay de diferente en estos amplificadores es cómo se hacen, y es lo que daremos en este artículo basado en application note de la propia Texas lnstruments

En un amplificador operacional la etapa más crítica es, sin duda, la de entrada.

Prácticamente son las características de los componentes de esta etapa que van a influir en el comportamiento del circuito a partir de la fuente de señal.

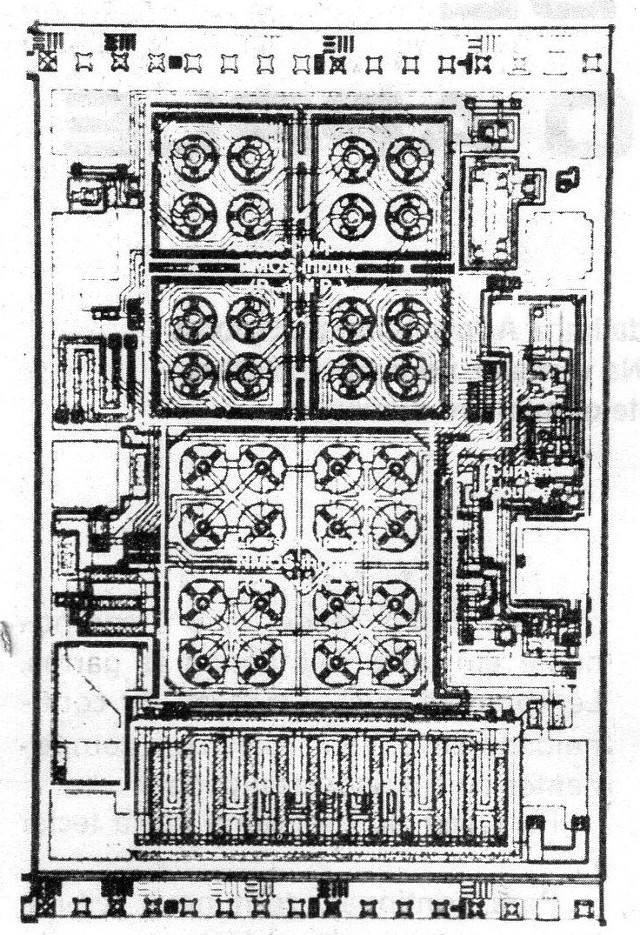

En la figura 1 tenemos una foto del "chip" del integrado CMOS de Texas tipo TLC271 que tomamos como referencia.

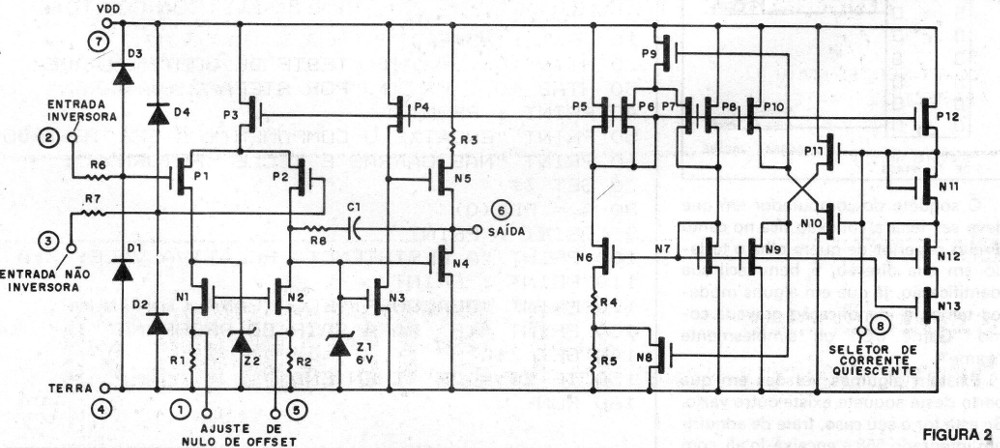

La etapa de entrada de este operacional está formada por transistores PMOS de entrada acoplados en cruz (P1 y P2) y pares de transistores NMOS formando un espejo de corriente (N1 y N2), todos ocupando la mitad del área del chip.

Los transistores de gran superficie son necesarios para haber la combinación de muchas pequeñas geometrías, posibilitando así que se obtenga un equilibrio crítico para el par de entrada.

Es muy importante obtener una perfecta boda de características de P1 y P2 para obtener un mínimo de offset y mayor estabilidad.

Para minimizar los efectos de las variaciones que ocurren durante el proceso de fabricación, los transistores P1, P2 y N1, N2 se fabrican en pequeñas secciones circulares ocupando grandes superficies y luego conectadas al chip para compensar las diferencias de dopaje.

Esta interconexión compleja minimiza los efectos del estrés mecánico y térmico en la estabilidad de la entrada, reduciendo así la tensión de offset.

Además, los niveles de umbral se mejor en cada par.

El diseño cuidadoso del chip, así como el particular proceso de Polsilicon-gate CMOS, llamado LinCMOS, son las claves para obtener en el chip bajo offset y gran estabilidad.

En el diagrama, el transistor P3 es la fuente de corriente constante para el par P1 y P2, mientras que P4 actúa como fuente de corriente constante de carga para el amplificador de tensión N3.

Aproximadamente la mitad de la ganancia de tensión viene de N3 y N4, mientras que la otra mitad viene de la combinación de P1, P3 y N2. (figura 2)

Proporcionando una salida de pequeñas señales tenemos el transistor N5 que está conectado como seguidor de tensión con el resistor de drenaje R3 y la fuente de polarización N4 (de baja conductividad).

La salida de señales intensas es drenada por N4 y limitada (protegida de cortos con Vdd) por un diodo zener Z1 que recorta la señal de la coma de N4 en torno a 6 V.

El diodo zener Z2 prevé desplazamientos de respuesta de los pasos de entrada en función de fugas con la temperatura.

La fuente de corriente constante de N5 está limitada por R3 que también tiene por función proteger contra cortocircuitos con la tierra el terminal de salida.

La duración máxima de los cortocircuitos se limita entonces a la capacidad de disipación de la envoltura DIP que es del orden de 1 W a una temperatura de 25 °C.

Para un Vdd de 10 V a temperatura ambiente, sin embargo, los cortos pueden tener una duración indefinida, sin peligro de daño al componente.

A partir del hecho de que la mitad de la ganancia viene de N3, la colocación de un capacitor de compensación de 12 pF a través de este transistor (de la compuesta de N3 a la fuente de N5) controla las eventuales desviaciones de comportamiento del circuito con señales de frecuencias elevadas, proporcionando así estabilidad contra una retroalimentación positiva y consecuentemente oscilaciones.

Otro 10% del área del chip está ocupado por el circuito que fija la corriente quiescente. El ajuste de cadena quiescente cubre tres décadas, de 10 a 1 000 uA. La conmutación entre las cadenas es hecha por los transistores P9 y N8.

Conectando el pin 8 a tierra tenemos la apertura de P9 y el cierre de N8 obteniendo el modo de corriente de más alto valor.

Conectando el pin 8 al Vdd tenemos el cierre de P9 y la apertura de N8, cuando se obtiene el suministro de corriente más bajo.

Cuando el perno 8 se mantiene flotante (o cuando se conecta a una fuente de tensión de al menos 0,8 V, o por debajo de Vdd), tanto P9 como N8 se cierran y tenemos el modo intermedio de suministro de corriente

Las llaves P9 y N8 seleccionan el modo de corriente de la siguiente manera: P9 conmuta P6 y P7 que actúa sobre el espejo de tensión CMOS, cambiando entonces la relación marca-espacio de P3 y P4 en relación al diodo P5 / P6.

Esto cambia la corriente de un factor de 10.

Por otro lado, N8 puede cambiar la resistencia en serie con la fuente de N6 cortocircuito R5 y haciendo así que la corriente de referencia en el diodo P5 / P6 cambie de una década.

La relación marca-espacio del canal de N6 es mayor que la de N7, pero la configuración en espejo que los dos transistores forman con P5 y P8 hace que las corrientes en N6 y N7 a valores iguales, lo que genera una tensión en R4 y R5 proporcional a kT / q, llevando entonces el dispositivo a una ventaja para los modos débiles de operación inversa.

Además, con R igual a R4 o R5, dependiendo del estado de N8, la referencia de corriente que fluye por P5 / P6 (diodo) es kT / qR que está determinada por la relación marca-espacio de N6 y N7.

El anillo de transistores formado por P12, N11, N12 y N13 estabiliza la fuente de media corriente por la actuación en el pin 8, por una tensión entre las barras de tensión de alimentación, conmutando los transistores N10 y PI1 y, consecuentemente, N8 y P9.

Estos cuatro transistores eliminan la necesidad del usuario de proveer un divisor de tensión (cuando en operación con fuente simple) para programar el modo de operación con corrientes medias.

Bibliografía: Texas Instruments Leading Electronícs Press Coverage - LinCMOS Technology: la nueva generación de Iinear Ics.